Data: 18 Luglio 2022

Il testo deve essere riconsegnato nella cartellina. Non è ammessa la consultazione degli appunti e dei compiti precedenti. Si possono consultare i data sheet. Non usare il colore rosso nello svolgimento.

#### ESERCIZIO N°1

5 punti

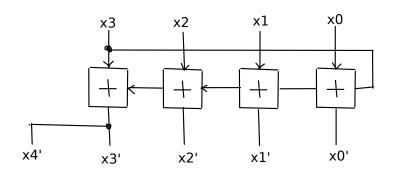

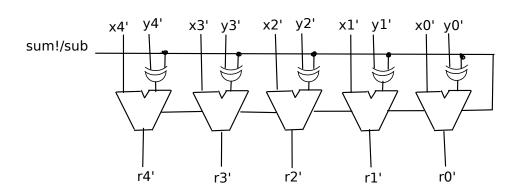

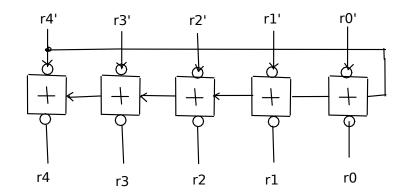

Progettare una rete combinatoria, facente uso di blocchi noti (porte logiche elementari, multiplexer, full-adder, ecc.) in grado di eseguire la somma o la sottrazione (su controllo si un segnale SUM!/SUB) di 2 numeri relativi a 4 bit, rappresentati in C1 e il cui risultato (per il risultato scegliere il numero di bit minimo che garantisce in ogni caso la rappresentabilità) sia pure rappresentato in C1.

## **ESERCIZIO N°2**

8 punti

Realizzare una subroutine per il microcontrollore AVR XMEGA256A3BU che valuta in R16 la parte intera della radice quadrata del valore senza segno contenuto in X (cioè nella coppia di registri R27:R26).

## **ESERCIZIO N°3**

5 punti

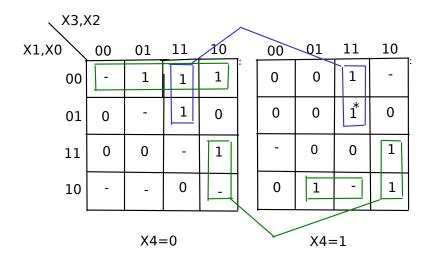

Realizzare in forma SP ottima una rete combinatoria a 5 ingressi ( $X_4$ ,  $X_3$ ,  $X_2$ ,  $X_1$  e  $X_0$ ) e una uscita non completamente definita, che ha la tabella di verità seguente:

Indicare tutti gli **implicanti essenziali** della funzione, evidenziando un mintermine che giustifica l'indicazione di essenziale.

## ESERCIZIO N°4

5 punti

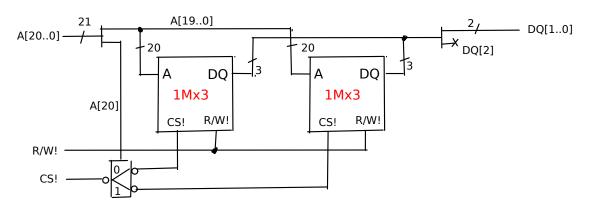

Avendo a disposizione chip di memoria SRAM da 1 M x 3 (costo  $0.30 \in$ ) e da 2 M x 5 (costo  $0.85 \in$ ), progettare un modulo di memoria da 4 M x 17 a costo minimo.

#### ESERCIZIO N°5

6 punti

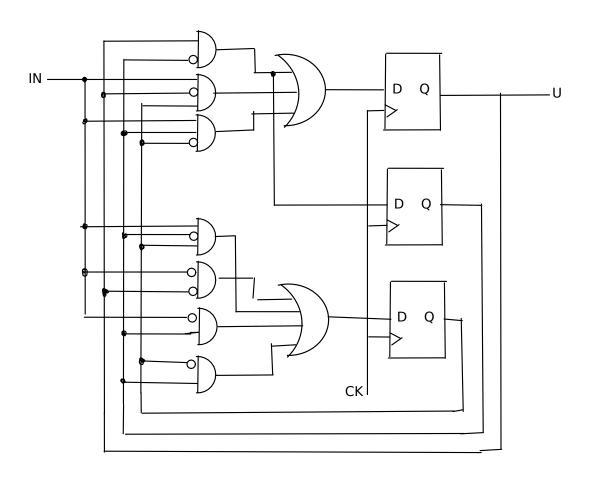

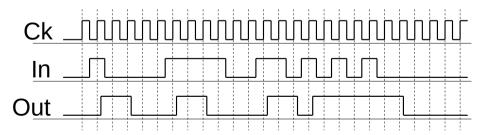

Disegnare lo schema logico di una macchina sequenziale sincrona secondo il modello di Moore con un ingresso e una uscita; quando la macchina rileva un fronte in salita dell'ingresso (campionato su 2 fronti di clock consecutivi) la macchina reagisce ponendo in uscita un impulso di 2 cicli di clock. La presenza di un ulteriore fronte durante l'impulso ne prolunga la durata, che si protrarrà in ogni caso per 2 cicli dopo l'ultimo fronte in salita rivelato in ingresso. Si hanno a disposizione D-FF e porte logiche elementari (AND, OR, NOT).

#### ESERCIZIO N°6

4 punti

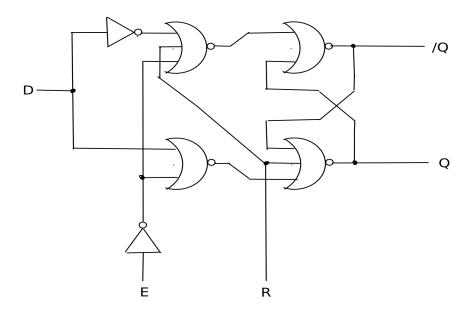

Disegnare lo schema logiche di un *D*-latch con abilitazione e reset prioritario, usando solo NOR (e NOT).

Analisi del range (C1) per somma-sottrazione Range degli operandi [-7..7] Range del risultato [-14..14]: sempre rappresentabile con 5 bit

Strategia: converto in C2, estendo, uso un comune somma-sottrattore, riconverto in C1

C1->C2+ext per entrambi gli operandi

somma-sottrattore in C2 a 5 bit

C2->C1 su 5 bit non si può avere OV

```

sqrt: //metodo per approx successive

push R0

push R1

push R17

clr R16

ldi R17,0b10000000 //tentativo iniziale

add R16,R17 //aggiunge al tentativo

mul R16,R16 //esegue il quadrato

cp XL,R0

cpc XH,R1

brcc s2

sub R16,R17 //tentativo abortito

s2:

Isr R17 //divide per 2

brne s1

pop R17

pop R1

pop R0

ret

```

| X3,   | K2 |     |    |    |   |    |     |    |    |

|-------|----|-----|----|----|---|----|-----|----|----|

| X1,X0 | 00 | 01  | 11 | 10 |   | 00 | 01  | 11 | 10 |

| 00    | 0  | 4   | 12 | 8  |   | 16 | 20  | 28 | 24 |

| 01    | 1  | 5   | 13 | 9  |   | 17 | 21  | 29 | 25 |

| 11    | 3  | 7   | 15 | 11 |   | 19 | 23  | 31 | 27 |

| 10    | 2  | 6   | 14 | 10 |   | 18 | 22  | 30 | 26 |

|       |    | X4= | =0 |    | , |    | X4= | =1 |    |

C'è un unico implicante essenziale; gli 1 rimanenti possono essere coperti con 3 implicanti principali (non essenziali), per un totale di 13 letterali (quello proposto non è l'unico modo).

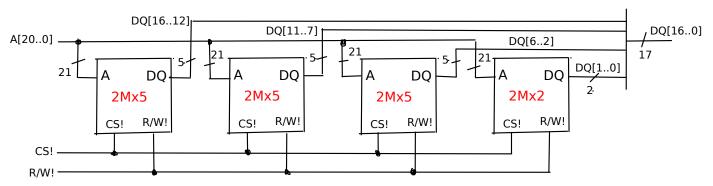

Eseguo inizialmente l'analisi dei costi, riconducendomi a sottomoduli con lo stesso numero di parole (4M) composti con i 2 tipi diversi di chip

A: 4Mx3 (1,20 €)

B: 4Mx5 (1,70 €); costo al bit minore

Combinazioni possibili per ottenere 4Mx17 e costo relativo

4B (3 bit in eccesso) 6,80 €3B+A (1 bit in eccesso) 6,30 € soluzione a costo minimo 2B+3A (2 bit in eccesso) 7,00 €B+4A (senza sprechi) 6,50 €

6A (1 bit in eccesso) 7,20 €

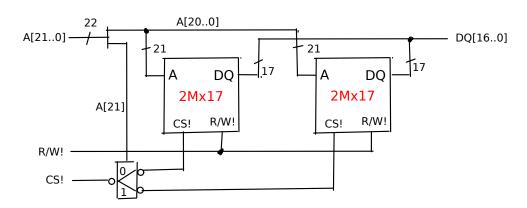

## Modulo da 2Mx2 (con 2 chip da 1Mx3)

## Modulo da 2Mx17 (con 3 chip da 2Mx5 e un modulo da 2Mx2)

### Modulo finale da 4Mx17 (con 2 moduli da 2Mx17)

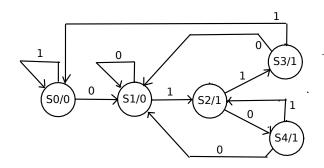

# Codifica degli stati (e rete per U)

|            | q2 | q1 | q0 | U |  |

|------------|----|----|----|---|--|

| S0         | 0  | 0  | 0  | 0 |  |

| S1         | 0  | 0  | 1  | 0 |  |

| <b>S2</b>  | 1  | 0  | 1  | 1 |  |

| <b>S</b> 3 | 1  | 1  | _  | 1 |  |

| S4         | 1  | 1  | 0  | 1 |  |

Con questa codifica U=q2

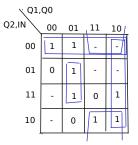

| Q1,Q0 |      |     |     |     |  |  |

|-------|------|-----|-----|-----|--|--|

| Q2,IN | . 00 | 01  | 11  | 10  |  |  |

| 00    | 001  | 001 |     |     |  |  |

| 01    | 000  | 101 |     |     |  |  |

| 11    |      | 111 | 000 | 101 |  |  |

| 10    |      | 110 | 001 | 001 |  |  |

| √Q1,Q0 |       |   |    |    |  |  |

|--------|-------|---|----|----|--|--|

| Q2,IN  | 00 01 |   | 11 | 10 |  |  |

| 00     | 0     | 0 | -  | -  |  |  |

| 01     | 0     | 1 | -  | -  |  |  |

| 11     | -     | 1 | 0  | 1  |  |  |

| 10     | -     | 1 | 0  | 0  |  |  |

| Q1,Q0 |       |   |    |    |  |  |

|-------|-------|---|----|----|--|--|

| Q2,IN | 00 01 |   | 11 | 10 |  |  |

| 00    | 0     | 0 | -  | -  |  |  |

| 01    | 0     | 0 | -  | -  |  |  |

| 11    | -     | 1 | 0  | 0  |  |  |

| 10    | -     | 1 | 0  | 0  |  |  |

D2=Q2Q1!+INQ2!Q0+INQ1Q0! D1=Q2 Q1! D0=IN! Q2!+IN! Q1+Q1 Q0!+IN Q1! Q0