SCHEDA ASE2504

Il testo deve essere riconsegnato nella cartellina. Non usare il colore rosso nello svolgimento.

#### **ESERCIZIO N°1**

8 punti

Realizzare un sottoprogramma per il microcontrollore XMEGA256A3BU che sostituisce il blocco di memoria contenuto tra gli indirizzi 0x2100 e 0x22FF (compresi gli estremi) con un nuovo blocco costituito da valori opposti a quelli originali, considerati espressi in modulo e segno su 8 bit. La subroutine deve, come al solito, lasciare inalterati tutti i registri.

Data: 11 Aprile 2025

#### ESERCIZIO N°2

5 punti

Determinare la rappresentazione binary32 (IEEE 754-2008) del numero  $-10^{-21}$  scegliendo il codice che minimizza l'errore relativo in modulo e calcolare tale errore.

Determinare poi la rappresentazione binary32 anche del cubo del numero dato.

### ESERCIZIO N°3

5 punti

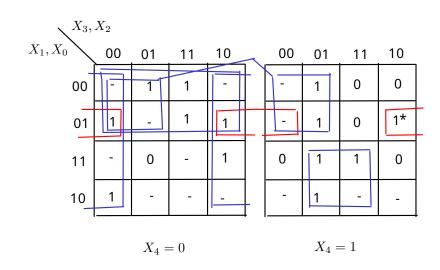

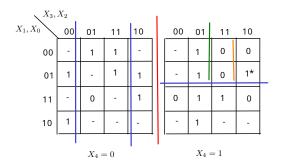

Realizzare in forma SP ottima la rete combinatoria a 5 ingressi,  $X_4$ ,  $X_3$ ,  $X_2$ ,  $X_1$ , e  $X_0$  e 1 uscita Y, la cui tabella di verità è la seguente: {-, 1, 1, -, 1, -, 0, -, 1, 1, 1, 1, -, -, -, -, -, 0, 1, 1, 1, 1, 0, 1, -, 0, 0, 0, -, 1}. Indicare gli implicanti essenziali, giustificando l'affermazione.

# ESERCIZIO N°4

5 punti

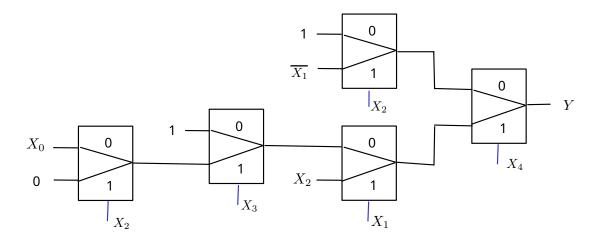

Realizzare la rete combinatoria dell'esercizio precedente facendo uso di mux 2:1, cercando di ridurne il numero, evitando l'uso di blocchi non necessari (duplicati, mux con ingressi identici, ecc.).

# **ESERCIZIO N°5**

5 punti

Disegnare lo schema logico di un contatore modulo 8 con abilitazione e controllo della direzione  $\overline{U}/D$ .

### **ESERCIZIO Nº6**

5 punti

Realizzare una macchina sequenziale sincrona secondo il modello di Moore, con 1 ingresso e 1 uscita che viene posta a 1 (dopo il clock) ogni volta che in ingresso viene riconosciuta una delle 2 seguenti sequenze: 1100 e 0011, non interallacciate in alcun modo.

```

/*Realizzare un sottoprogramma per il microcontrollore XMEGA256A3BU che

sostituisce il blocco di memoria contenuto tra gli indirizzi

0x2100 e 0x22FF (compresi gli estremi) con un nuovo blocco

costituito da valori opposti a quelli originali,

considerati espressi in modulo e segno su 8 bit.

La subroutine deve, come al solito, lasciare inalterati tutti i registri.*/

block_MSinvert:

push R16

push XL

push XH

//usa X come primo puntatore e lo inizializza a 0x2100

ldi XL, low(0x2100)

ldi XH, high(0x2100)

loop:

ld R16, X

subi R16,128

//questa operazione commuta solo il bit 7 (del segno)

st X+,R16

//rimette a posto il valore cambiato di segno

cpi XL, low(0x22FF+1)

brne loop

cpi XH,high(0x22FF+1)

brne loop

pop XH

pop XL

pop R16

ret

```

Determinare la rappresentazione binary32 (IEEE 754-2008) del numero A dato, scegliendo il codice che minimizza l'errore relativo in modulo e calcolare tale errore.

Determinare poi la rappresentazione binary32 del cubo di A.

$$A = -10^{-21} \simeq -2^{-70} (1 + 1514912 \cdot 2^{-23})$$

Quindi S=1, E=e+127=0x39, T=0x171DA0

A: 1 00111001 001 0111 0001 1101 1010 0000

L'errore relativo è

$$1 - \frac{\hat{A}}{A} \simeq 3,17 \cdot 10^{-8}$$

Il cubo di A non è rappresentabile in modo normalizzato. Quindi occorre ricorrere alla legge di rappresentazione dei sottonormali.

$$A^3 = -10^{-63}$$

ma, essendo

$$10^{-63} = (10^3)^{-21} \simeq (2^{10})^{-21} \ll 2^{-149}$$

La rappresentazione più vicina in binary32 è -0. Quindi S=1, E=0, T=0

1

Realizzare in forma SP ottima la rete combinatoria a 5 ingressi e 1 uscita, la cui tabella di verità è la seguente:  $\{-, 1, 1, -, -, -, 0, -, 1, -, 1, 1, 1, -, -, -, -, 0, 1, 1, 1, 1, 0, 1, -, 0, 0, 0, -, 1\}$ . Indicare gli implicanti essenziali, giustificando l'affermazione.

$$Y = \overline{X_2} \, \overline{X_1} X_0 + \overline{X_3} \, \overline{X_1} + \overline{X_4} \, \overline{X_1} + \overline{X_4} \, \overline{X_2} + X_4 X_2 X_1$$

La funzione può essere espressa dalla somma di 5 implicanti, di cui uno solo è essenziale (con  $^*$ ). I letterali necessari sono 12 (e ci sono diverse altre soluzioni ottime).

Realizzare la rete combinatoria dell'esercizio precedente facendo uso di mux 2:1, cercando di ridurne il numero, evitando l'uso di blocchi non necessari (duplicati, mux con ingressi identici, ecc.).

Possiamo proporre una realizzazione, con riferimento alla mappa:

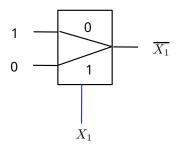

Per realizzare la negazione, utilizzo un ulteriore MUX

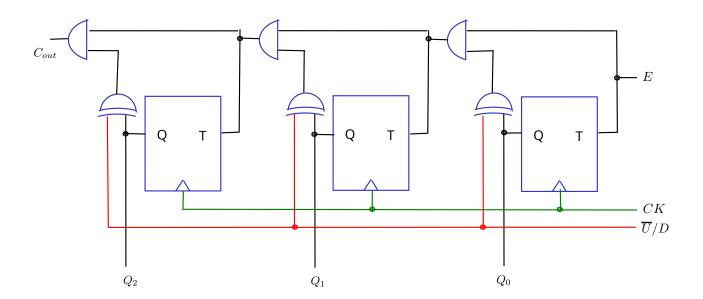

Disegnare lo schema logico di un contatore modulo 8 con abilitazione e controllo della direzione.

6

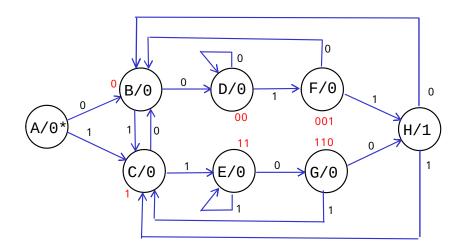

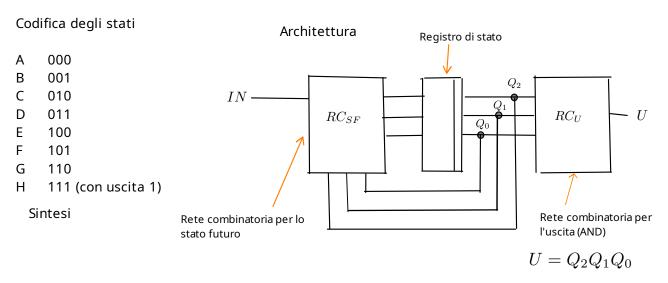

Realizzare una macchina sequenziale sincrona secondo il modello di Moore, con 1 ingresso e 1 uscita che viene posta a 1 (dopo il clock) ogni volta che in ingresso viene riconosciuta una delle 2 seguenti sequenze: 1100 e 0011, non interallacciate in alcun modo.

| 1 |   |   |   |   |

|---|---|---|---|---|

|   | 0 | 0 | 0 | 0 |

|   | 0 | 0 | 1 | 1 |

|   | 1 | 1 | 0 | 0 |

| _ | 1 | 0 | 0 | 1 |

|   | _ |   |   |   |

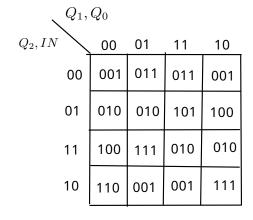

$$D_2 = IN\overline{Q_2}Q_1 + INQ_2\overline{Q_1} + \overline{IN}Q_2\overline{Q_0}$$

|   | 0 | 1 | 1 | 0 |   |

|---|---|---|---|---|---|

|   | 1 | 1 | 0 | 0 |   |

|   | 0 | 1 | 1 | 1 |   |

| _ | 1 | 0 | 0 | 1 | Г |

$$\begin{split} D_1 &= \overline{IN} \; \overline{Q_2} Q_0 + \overline{IN} \overline{Q_2} \; \overline{Q_1} + IN Q_2 Q_0 + \\ &+ IN Q_2 Q_1 + \overline{IN} Q_2 \overline{Q_0} \end{split}$$

$$D_0 = \overline{IN} \, \overline{Q_2} + \overline{Q_2} Q_1 Q_0 + Q_2 \overline{Q_1} Q_0 + \overline{IN} Q_1$$