| SCHEDA N°D_04_01                        |                                                                                                                                                                                                |           | Data: |             |  |

|-----------------------------------------|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|-----------|-------|-------------|--|

| Cognome                                 |                                                                                                                                                                                                | Posizione |       | Valutazione |  |

| Nome                                    |                                                                                                                                                                                                |           |       |             |  |

| Tempo disponibile:<br>Durante la prova: | 1ora NON è consentito uscire dall'aula, né consultare testi esclusi i data sheet NON usare il colore rosso Riconsegnare tutti i fogli ricevuti. I risultati devono essere motivati chiaramente |           |       |             |  |

## ESERCIZIO Nº1

7 punti

Determinare i margini di rumore  $MN_{\rm H}$  e  $NM_{\rm L}$  per un invertitore RTL. Per l'alimentazione si ha  $V_{\rm CC} = 5$  V, per le resistenze di base e di collettore si ha  $R_{\rm B} = 12$  k $\Omega$ ,  $R_{\rm C} = 1.8$  k $\Omega$  e per il transistore  $V_{\rm BE(on)} = 0.7$  V,  $V_{\rm BE(sat)} = 0.8$  V,  $V_{\rm CE(sat)} = 0.1$  V,  $N_{\rm BE} = 150$

## ESERCIZIO N°2

6 punti

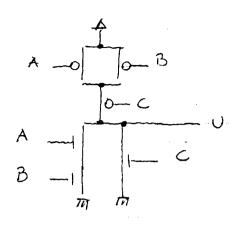

Realizzare in tecnologia CMOS un circuito digitale a 3 ingressi A, B e C e un'uscita U che implementi la funzione logica U = C'(A' + B')

## ESERCIZIO N°3

7 punti

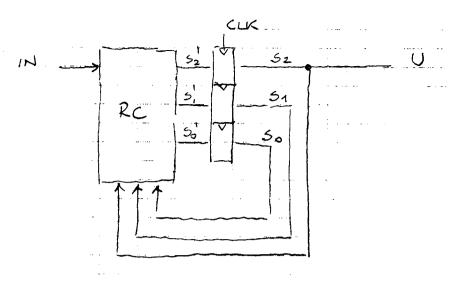

Disegnare il grafo di flusso e progettare la rete sequenziale di Moore che lo implementa, di un sistema sequenziale con un ingresso e una uscita, che viene posta a 1 ogni volta che l'ingresso commuta due volte di seguito. A titolo di esempio viene presentata l'uscita della rete (dopo il clock) per una possibile sequenza di ingresso:

IN 000100100101010100010 OUT XX00100100111111110001

#### ESERCIZIO N°4

5 punti

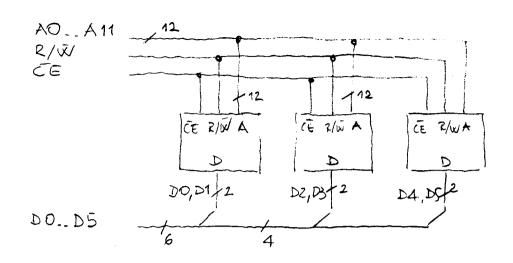

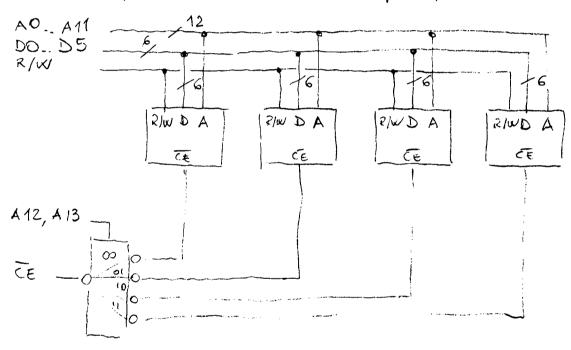

Si supponga di avere a disposizione moduli di memoria RAM da  $4k \times 2$ . Disegnare un loro possibile assemblaggio che realizzi un modulo da  $16k \times 6$ .

## ESERCIZIO N°5

8 punti

Scrivere un programma per il microcontrollore AT90S8515 che, dopo avere correttamente inizializzato le porte, legga continuamente lo stato degli 8 pin della porta A e ponga in uscita sulla porta B un numero binario corrispondente al numero di pin della porta A trovati al valore 1.

| PORTA A (IN) | PORTA B (OUT) |  |  |  |

|--------------|---------------|--|--|--|

| 00101001     | 00000011      |  |  |  |

| 10111011     | 00000110      |  |  |  |

| 00000000     | 00000000      |  |  |  |

| 11111111     | 00001000      |  |  |  |

# SCHEDA DO4. 01 ELETTRONICA

Si ricova subito:

$$V_{IL} = 0.7V$$

$V_{OL} = 0.1V$  (satura)

$V_{OH} = 5V$  (interdetta)

Occorre déterminare VIH. Mi pougo mel pourts évuite tra soturatione e toua attive. Cioè dove si les:

Ricaro

Per volori di ingresso magnori, le I3 crexe, mentre le Ic non può che restore costante. Quindi si confermo che a è soturo

Suriue

3 udividus un possibile groß di fluxo

Occorrono 3 variabili di stato (6 stati): 525,50 Scelgo una codifica degli stati

Tabella di fluss

| 12       | 0 | 11 | _ U |

|----------|---|----|-----|

| Α.       | B | E  | 1   |

| B        | C | A  | 1   |

| <b>C</b> |   | D  | ٥   |

| D        | B | E  | 0   |

| E        | F | E  | Ø   |

| F        | _ | A  | 0   |

Modella per la macchine di Moore la coolifica degli Boti è stata scelta in mools che 5, = U

Simetizzo le rete combinatoria

| 117                                    | 52   |     |      |     |

|----------------------------------------|------|-----|------|-----|

| 5, 50                                  | 00   | 01  | 11   | 10  |

| 00                                     | 000  | ×   | ×    | 001 |

| 01                                     | 110  | 110 | 011  | 011 |

| ······································ | 010  | ×   | ··-× | 011 |

| 10                                     | ರಿರು | 000 | 101  | 101 |

$$0 \times \times 0$$

$$0 \times \times 0$$

$$0 \times \times 0$$

$$0 \times \times 0$$

$$0 \times 0$$

Rete per 51

$$0 \times \times 0$$

$$1 + 1 + 1$$

$$1 \times \times 1$$

$$0 = 5_0$$

Rever per 50

$$0 \times \times 1$$

$0 \times \times 1$

$0 \times \times 1$

$0 \times \times 1$

$0 \times \times 1$

Rollizzo prima un 4k×6 con 3 dip 4k×2

(4)

Assemblo poi 4 moduli 4kx6 per fore il 16kx6

5 progr: CLR R16

OUT DDRA, R16

SER R16

OUT DDRB, R16

OUT PORTA, R16

ciclo: IN RIG, PINA

CLR RIT

LDI R18,8

e1: LSL R16

INC RIT

DEC R18

BRNE e1

OUT PORT B, RIT

RTMP ciceó

; conta e partire del MSB