| SCHEDA N°D_04_02                        |                                                                                                                                                                                                 |           | Data: |             |  |

|-----------------------------------------|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|-----------|-------|-------------|--|

| Cognome CORRELIONE  Nome                |                                                                                                                                                                                                 | Posizione |       | Valutazione |  |

| Tempo disponibile:<br>Durante la prova: | 1ora NON è consentito uscire dall'aula, né consultare testi esclusi i data sheet NON usare il colore rosso Riconsegnare tutti i fogli ricevuti. I risultati devono essere motivati chiaramente. |           |       |             |  |

# **ESERCIZIO Nº1**

7 punti

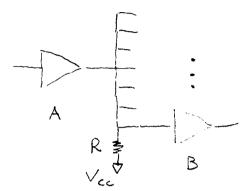

Si considerino le famiglie logiche A e B, i cui parametri elettrici sono riportati nel seguito. Si vogliono collegare 7 inverter della famiglia logica B in uscita a un inverter della famiglia logica A. Determinare, se possibile, una configurazione circuitale che permetta tale connessione. Si assuma di avere a disposizione una tensione di alimentazione  $V_{\rm CC} = 5$  V e resistenze di valore opportuno.

| Pai            | rametri di usc  | ita della log  | ica A         |

|----------------|-----------------|----------------|---------------|

| $V_{ m OLmax}$ | 0.8 V           | $V_{ m OHmin}$ | 3 V           |

| $I_{ m OLmax}$ | 10 mA           | $I_{ m OHmin}$ | -10 mA        |

| Para           | ametri di ingre | esso della lo  | gica <i>B</i> |

| $V_{IL}$       | 1.5 V           | $V_{ m IH}$    | 3.5 V         |

| $I_{ m IL}$    | -0.5 mA         | $I_{ m IH}$    | 0.1 mA        |

### **ESERCIZIO Nº2**

6 punti

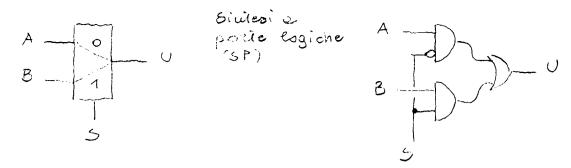

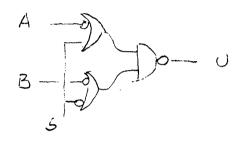

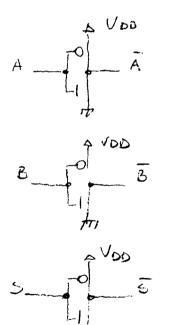

Realizzare in tecnologia CMOS un multiplexer a due vie.

## **ESERCIZIO N°3**

7 punti

Disegnare il grafo di flusso di un contatore bidirezionale (U/D') con reset (RES) modulo 4 e progettare la rete sequenziale di Moore che lo implementa. A titolo di esempio viene presentata l'uscita della rete (dopo il clock) per una possibile sequenza degli ingressi:

| RES | U/D' | C1 | CO   |

|-----|------|----|------|

| 1   | 0    | 0  | 0    |

| 1   | 1    | 0  | 0    |

| 0   | 1    | 0  | 1    |

| 0   | 1    | 1  | 0    |

| 0   | 1    | 1  | 1    |

| 0   | 1    | 0  | 0    |

| 0   | 0    | 1  | 1    |

| 1   | 0    | 0  | 0    |

| 0   | 0    | 1  | 1    |

| 0   | 0    | 1  | 0, , |

#### **ESERCIZIO Nº4**

5 punti

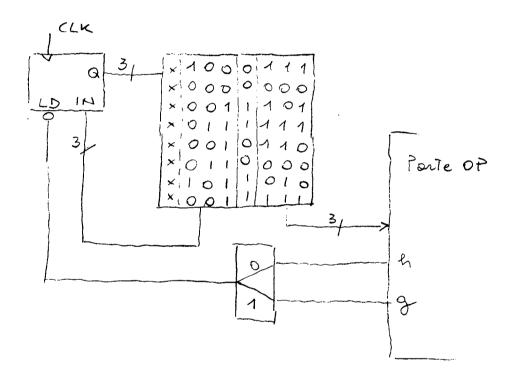

Disegnare lo schema logico di un sequencer a 8 stati che implementa il seguente microcodice. Si assegni un codice di tre bit agli stati e si mostri il contenuto della ROM da 8 parole di 8 bit; come registro per l'indirizzo si ha a disposizione un contatore sincrono con caricamento parallelo (se il segnale di ingresso sincrono LD è attivo carica parallelo, altrimenti incrementa modulo 8).

```

A1: OP=111; IF h A2 ELSE A5

A2: OP=000; IF h A3 ELSE A1

A3: OP=101; IF g A4 ELSE A2

A4: OP=111; IF g A5 ELSE A4

A5: OP=110; IF h A6 ELSE A2

A6: OP=000; IF h A7 ELSE A4

A7: OP=010; IF g A8 ELSE A6

A8: OP=111; IF g A1 ELSE A2

```

#### ESERCIZIO N°5

8 punti

Scrivere un sottoprogramma per il microcontrollore AT90S8515 che complementi i bit di posizione 3 e 5 (LSB ha posizione 0) della locazione di memoria puntata dal registro X. Valutare il numero di cicli che richiede l'esecuzione del sottoprogramma scritto, compresa la sua chiamata.

1 le logiche nou sous interfacciobili direttamente

Provo à risolère il problema con un puel-up

Détermino le condizioni che deve soddisfare il circuito Sue eivele boso

Volume < VIL OK

Ioumex > Vcc - Volumex - NIIL de ani

R> Vcc- Vol max = 4.2 K = 0.646 K \( \Omega\) = 10-3.5

Sul livello ello il pull up deve gerentire elmeno VIII. Ipotizzo interolitia ea parta A.

Vcc - VIH > NIIH de aui

$R \times \frac{V_{CC} - V_{IH}}{NI_{IH}} = \frac{1.5 \text{ K}}{0.7} = 2.14 \text{ K} \Omega$

la salutione quindi esiste. Si può sagaiere, per esempio

2 = 1 KSZ

Modifico la siviesi in mode da riportarui ell'uso di una porta AOI

Redizzo in CHOS

3

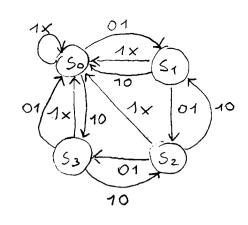

Grafo de fenoso (2, U/D')

Coolifico gli stati in modo de realizzare la rete di uscita con un costocizanito

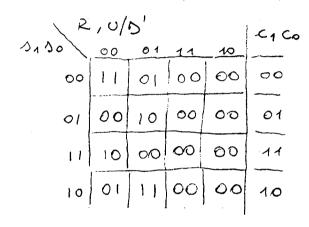

Del grafo ricavo la tabella di fenso

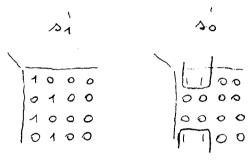

$$S_{1} = \overline{R} \cdot \overline{U/D'} \cdot \overline{S_{1}} \cdot \overline{S_{0}} +$$

$$+ \overline{Q} \cdot \overline{U/D'} \cdot \overline{S_{1}} \cdot \overline{S_{0}} +$$

$$+ \overline{R} \cdot \overline{U/D'} \cdot \overline{S_{1}} \cdot \overline{S_{0}} +$$

$$+ \overline{R} \cdot \overline{U/D'} \cdot \overline{S_{1}} \cdot \overline{S_{0}}$$

$$S_{0} = \overline{R} \cdot \overline{S_{0}}$$

Sequenzialore a contaiore Codifica degli otari e per il mux dei plag

```

A7

000

AZ

001

A3

010

A4

011

AS

100

A6

101

A 7

110

A 8

111

```

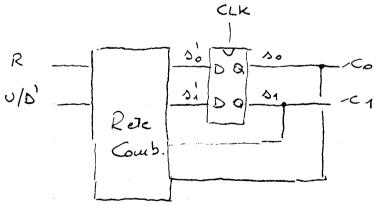

Architettura

5 6: to

3 RCALL subz

```

2

2

FUSH R16

subz:

PUSH R17

2

LD R16, X

LDI R17, 0500101000

EOR R16, R17

1

7

2

5T

X, Ŕ16

R17

2

POP

2

POP R16

RET

```

Sommendo i cicli si ottiene 21