| SCHEDA <b>D10_04</b> |      | Data: <b>12 Aprile 2010</b> |  |

|----------------------|------|-----------------------------|--|

| Cognome              | Nome | Matricola                   |  |

|                      |      |                             |  |

## ESERCIZIO N°1

7 punti

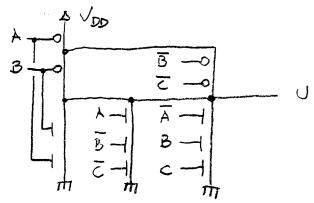

**Determinare** la tabella di verità del seguente circuito logico CMOS facendo ricorso ai valori 0, 1, Z e X, con l'usuale significato. Valutare quindi per ogni caso in cui l'uscita è indeterminata (X) il valore della corrente assorbita dall'alimentazione. ( $V_{DD} = 5 \text{ V}$ ;  $V_{Tn} = |V_{Tp}| = 1 \text{ V}$ ;  $k_n = |k_p| = 6 \text{ mA/V}^2$ ).

### ESERCIZIO N°2

6 punti

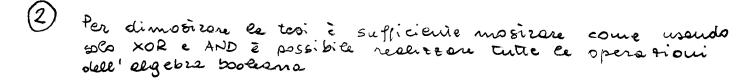

Dimostrare che è possibile realizzare ogni possibile rete combinatoria usando solamente porte di tipo AND e XOR.

## ESERCIZIO N°3

6 punti

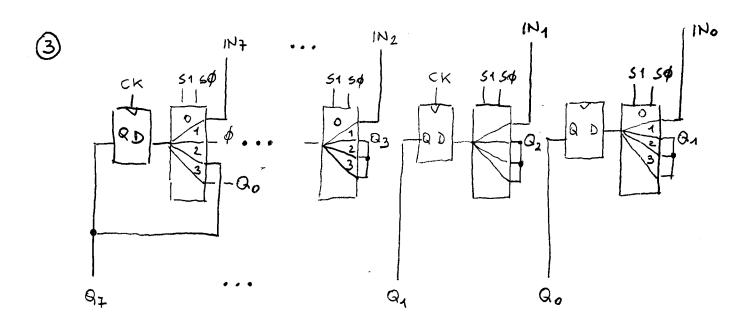

**Realizzare** un registro a 8 bit con 2 segnali di controllo in grado di eseguire le seguenti operazioni: **0)** caricamento parallelo 1) shift destro logico 2) shift destro aritmetico 3) rotazione destra.

# **ESERCIZIO Nº4**

6 punti

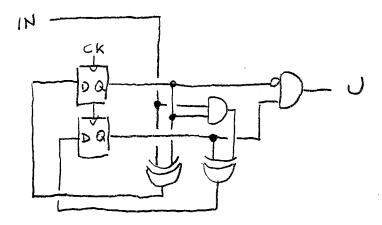

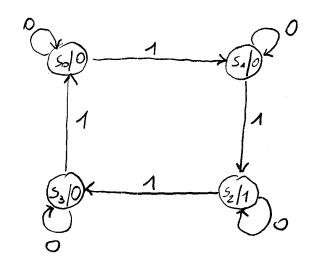

Determinare tipologia architetturale e ricavare il grafo di flusso della seguente macchina sincrona.

### **ESERCIZIO N°5**

8 punti

Realizzare un programma per il microcontrollore AT90S8515 che presenti in uscita alla porta B una sequenza di conteggio modulo 60. L'uscita deve essere aggiornata regolarmente al nuovo valore ogni 10 cicli di clock del processore. La pressione di un pulsante collegato tra il pin A0 e massa deve agire sul conteggio come un reset.

Détermins reparatamente la funzione della parte NMOS e PMOS

| ABC | LNMOS | PHOS | ) 0 |

|-----|-------|------|-----|

| 000 | OFF   | ON   | 1   |

| 001 | OFF   | 43   | 1   |

| 010 | OFF   | OFF  | 2   |

| 011 | 97    | 64   | ×   |

| 100 | 07    | 040  | 0   |

| 101 | OFF   | OFF  | 2   |

| 110 | 02    | OFF  | Ō   |

| 111 | 07    | OFF  | Ö   |

Mell'unico sieto in cui scorre correire (x), con A=0, A=1, C=1 si ho

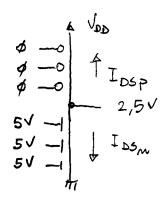

Vista la "simmetria" dei MOS si avrà Vo=2,5V e tutti i MOS in tona triodo.

l tre mos in serie equivalgous a un unico ros con K = K/3(hanno la siena Vr e Va)

Quindi  $I_{DD} = I_{DSU} = \frac{Km}{6} \frac{V_{DD}}{2} \left( V_{DD} + \frac{V_{DD}}{2} - 2V_{TM} \right) = 13,75 \text{ mA}$

NOT: A 1

AND: A -B

Regisiro universale: 51,50 einer di controllo 1N[7.0] ingresso parallela Q[7.0] velore di uscita (4) la marchine presente l'architettura di MOORE: e'uscita di pende selo dello stato

le grafo è il seguence (conseivre modules 4) con abile.)

|                      | 19,  | 90   | U    |  |  |

|----------------------|------|------|------|--|--|

| 50<br>51<br>52<br>53 | 0011 | 0101 | 0010 |  |  |

| codifica             |      |      |      |  |  |

# 5 Programme

```

CLR R16

SER R17

OUT DDRA, RIG

; ingresso

OUT PORTA, RIT

OUT DORB, RIT

; pull-up ou

; uscite

eap: OUT PORTB, RIG

7000

; toute NOP (3) per

; arrivere a 10 cicli

R16

2

INC

3

RIG, 60

CPI

5

BRNE e1

CLR RIG

e1: RJMP eoop

; 7

```