| SCHEDA | D24 | 02 |

|--------|-----|----|

Il testo va riconsegnato

# **ESERCIZIO N°1**

8 punti

Scrivere un sottoprogramma nel linguaggio assembly della famiglia XMEGA AVR che trova quanti multipli di 16 sono contenuti nelle locazioni di memoria da 0x3000 a 0x33FF (compresi gli estremi) e lascia il risultato nella coppia di registri R25:R24.

Data: 25 Gennaio 2024

### **ESERCIZIO N°2**

6 punti

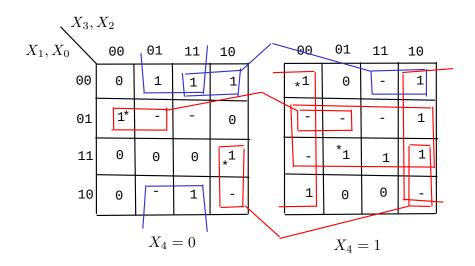

Realizzare in forma SP ottima la rete combinatoria a 5 ingressi  $X_4$ ,  $X_3$ ,  $X_2$ ,  $X_1$ ,  $X_0$  e una uscita U definita dalla seguente tabella di verità

{0; 1; 0; 0; 1; -; -; 0; 1; 0; -; 1; 1; -; 1; 0; 1; -; 1; -; 0; -; 0; 1; 1; 1; -; 1; -; 0; 1}. Indicare quali implicanti sono essenziali, motivando la scelta.

## **ESERCIZIO N°3**

6 punti

Spiegare la differenza tra le istruzioni FMUL, FMULS e FMULSU del linguaggio assembly della famiglia AVR, indicare la collocazione del risultato e calcolare il valore in base 10 del risultato frazionale [1.15] (con o senza segno in funzione del tipo di risultato prodotto), delle tre diverse istruzioni quando gli argomenti sono due registri il cui contenuto è rispettivamente 0xBF e 0xFC.

## **ESERCIZIO N°4**

6 punti

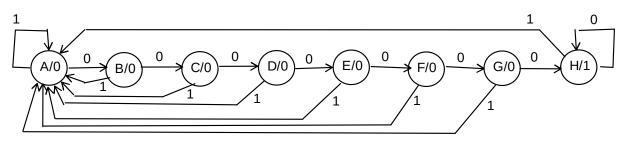

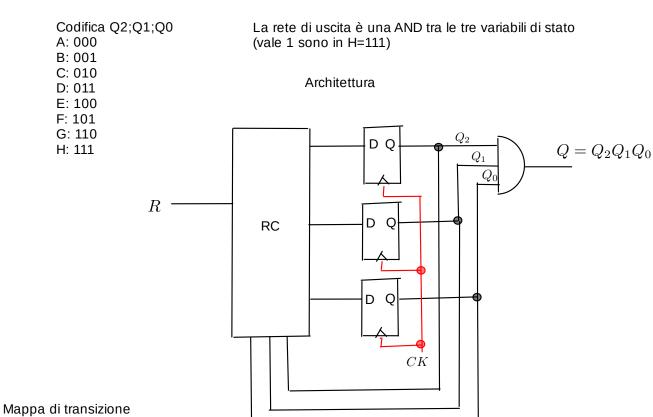

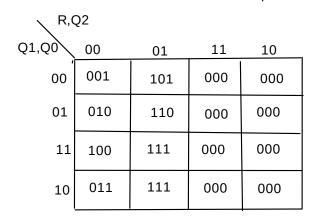

Progettare una rete di Moore con il solo ingresso di reset sincrono *R* e una uscita *Q* che vale 0 per 7 periodi di clock dopo un reset e poi resta permanentemente a 1 fino al reset successivo.

### ESERCIZIO N°5

7 punti

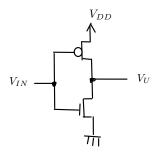

Individuare il valore della tensione di uscita di una porta NOT CMOS a vuoto, quando l'ingresso vale 0 e quando vale 2/3  $V_{DD}$ .

$(V_{DD} = 3.3 \text{ V}; V_{Tn} = |V_{Tp}| = 0.8 \text{ V}; k_n = |k_p| = 4 \text{ mA/V}^2)$

```

/*Scrivere un sottoprogramma nel linguaggio assembly della famiglia

XMEGA AVR che trova quanti multipli di 16 sono contenuti

nelle locazioni di memoria da 0x3000 a 0x33FF (compresi gli estremi)

e lascia il risultato nella coppia di registri R25:R24.*/

write_7n:

//variabile di appoggio

push R16

push XL

push XH

//per il risultato

clr R24

clr R25

ldi XL, low(0x3000)

ldi XH, high(0x3000)

loop:

ld R16, X+

//i multipli di 16 hanno 4 zeri in fondo

andi R16,0x0F

brne no_16n

adiw R25:R24,1

no_16n

cpi XL, low(0x3400) //test di fine ciclo con 0x33FF+1

brne loop

cpi XH, high(0x3400)

brne loop

pop XH

pop XL

pop R16

ret

```

Realizzare in forma SP ottima la rete combinatoria a 5 ingressi X4, X3, X2, X1, X0 e una uscita U definita dalla seguente tabella di verità  $\{0; 1; 0; 0; 1; -; -; 0; 1; 0; -; 1; 1; -; 1; 0; 1; -; 0; -; 0; 1; 1; 1; -; 1; -; 0; 1\}$ . Indicare quali implicanti sono essenziali, motivando la scelta.

$$U = \overline{X_3} \, \overline{X_1} X_0 + X_3 \, \overline{X_2} X_1 + X_4 \overline{X_2} + X_4 X_0 + \overline{X_4} X_2 \overline{X_0} + X_3 \overline{X_1} \, \overline{X_0}$$

I primi 4 implicanti (in rosso nella mappa) sono essenziali e con l'asterisco è evidenziato un mintermine che li rende tali.

Spiegare la differenza tra le istruzioni FMUL, FMULS e FMULSU del linguaggio assembly della famiglia AVR, indicare la collocazione del risultato e calcolare il valore in base 10 del risultato frazionale [1.15] (con o senza segno in funzione del tipo di risultato prodotto), delle tre diverse istruzioni quando gli argomenti sono due registri il cui contenuto è rispettivamente 0xBF e 0xFC.

Le tre istruzioni eseguono la moltiplicazione tra grandezze contenute in due registri interpretate come frazionali [1.8] e pongono il risultato su 16 bit nella coppia di registri R1:R0 come [1.15].

Gli operandi vengono interpretati diversamente dalle 3 operazioni e presentano pure delle limitazioni.

#### FMUL Rd.Rr

Gli operandi sono numeri frazionali binari senza segno e possono essere registri nel range R16-R23

### FMULS Rd, Rr

Gli operandi sono numeri frazionali con segno C2 e possono essere registri nel range R16-R23

### FMULSU Rd, Rr

Rd è un numero frazionale con segno (C2) e Rr senza segno. Gli operandi possono essere registri nel range R16-R23

In tutti i casi viene modificato il flag C, che assume il valore del bit più significativo del risultato.

I valori assegnati, in base 10, corrispondono ai numeri frazionali senza segno Rd=0xBF=1,4921875; Rr=0xFC=1,96875 con segno Rd=0xBF=-0,5078125; Rr=0xFC=-0,03125

### quindi

FMUL Rd,Rr // in R1:R0 viene 0,937744140625 con C=1 FMULS Rd,Rr // in R1:R0 viene 0,015869140625 FMULSU Rd,Rr // in R1:R0 viene -0,999755859375

Progettare una rete di Moore con il solo ingresso di reset sincrono R e una uscita Q che vale 0 per 7 periodi di clock dopo un reset e poi resta permanentemente a 1 fino al reset successivo.

### Grafo della macchina

| 0             | 1             | 0                | 0             |                                              |

|---------------|---------------|------------------|---------------|----------------------------------------------|

| 0             | 1             | 0<br>0<br>0<br>0 | 0             | $Q_2 = \overline{R}Q_2 + \overline{R}Q_1Q_0$ |

| \1            | 1             | 0                | 0             |                                              |

| 0             | 1             | 0                | 0             |                                              |

|               |               |                  |               | _                                            |

| $\overline{}$ | $\overline{}$ | Λ                | $\overline{}$ | ]                                            |

| 0 0 0 0                       |                                                                                                    |

|-------------------------------|----------------------------------------------------------------------------------------------------|

| 1 1 0 0                       | $Q_1 = \overline{R} \ \overline{Q_1} Q_0 + \overline{R} Q_2 Q_1 + \overline{R} Q_1 \overline{Q_0}$ |

| 0 1 0 0                       |                                                                                                    |

| 1 1 0 0<br>0 1 0 0<br>1 1 0 0 |                                                                                                    |

| 1 |   |   |   |   |

|---|---|---|---|---|

| 1 | 1 | 0 | 0 | l |

| 0 | 0 | 0 | 0 | l |

| 0 | 1 | 0 | 0 |   |

| 1 | 1 | 0 | 0 |   |

| - |   |   |   | • |

$$Q_0 = \overline{R} \, \overline{Q_0} + \overline{R} Q_2 Q_1$$

Individuare il valore della tensione di uscita di una porta NOT CMOS a vuoto, quando l'ingresso vale 0 e quando vale 2/3 VDD.

$$V_{DD} = 3,3 \text{ V}; \quad V_{Tn} = |V_{Tp}| = 0,8 \text{ V}; \quad k_n = |k_p| = 4 \text{ mA/V}^2$$

Quando l'ingresso VIN=0, il pMOS è triodo e l'nMOS è interdetto. L'uscita è VDD e dall'alimentazione non scorre alcuna corrente.

Quando VIN=2/3VDD, sono accesi entrambi i MOS. Data la simmetria dei componenti e poiché l'ingresso è maggiore di VDD/2, si ha nMOS triodo e pMOS saturo. Quindi si può trovare la corrente erogata dall'alimentazione.

$$I_{DD} = I_{SDp} = \frac{|k_p|}{2} (V_{IN} - V_{DD} - V_{Tp})^2 = 0,18 \text{ mA}$$

Scriviamo l'equazione KCL al nodo di uscita con l'nMOS triodo, usando VU come incognita.

$$I_{DD} = I_{DSn} = \frac{k_n}{2} V_U (2V_{IN} - V_U - 2V_{Tn})$$

$$2x^2 - 5,6x + 0,18 = 0$$

Risolvendo si ottengono 2 soluzioni (una maggiore di VDD/2 non accettabile), di cui quella valida è

$$V_U = 32,52 \text{ mV}$$