| SCHEDA <b>ASE1502</b> (di allenamento) |  | Data: <b>31 Gennaio 2015</b> |  |  |

|----------------------------------------|--|------------------------------|--|--|

| Cognome                                |  | Nome                         |  |  |

# ESERCIZIO Nº1

6 punti

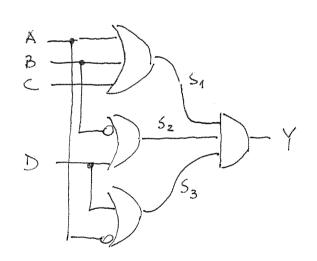

a) Determinare la mappa di Karnaugh della funzione logica Y corrispondente alla seguente espressione booleana.

$[(\overline{A+B})C] \oplus [\overline{AD} + B(A+\overline{C})] \oplus \overline{BD}$

- **b)** Realizzare con porte logiche elementari in forma PS a minimo numero di letterali la funzione del punto a).

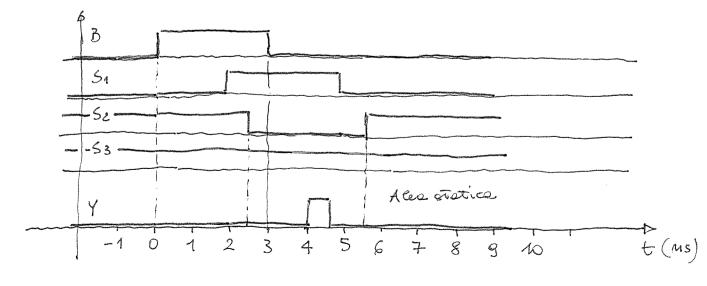

- c) Se porte logiche elementari (AND, OR, NOT) a K ingressi hanno  $T_{pd}$  = 0,5 ns + 0,5 K ns disegnare nel tempo la risposta Y della porta a un impulso rettangolare di 3 ns della variabile B, quando tutti gli altri ingressi mantengono un valore nullo. Si assuma per le ascisse una scala di 2 ns/quadretto.

#### ESERCIZIO N°2

5 punti

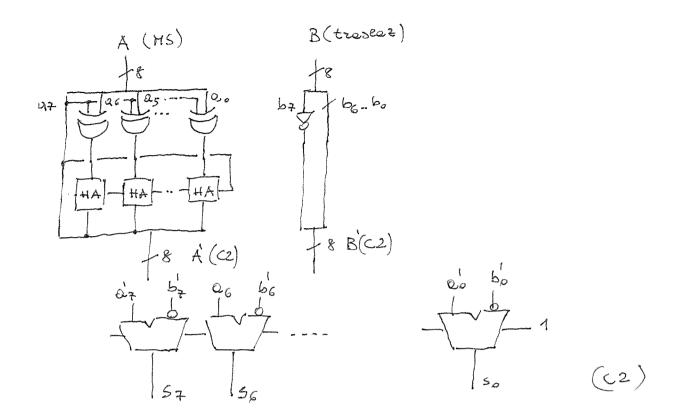

- a) Usando blocchi logici noti (porte logiche elementari, full-adder, mux e demux...) realizzare una rete in grado di sottrarre in virgola fissa a 8 bit un numero in traslazione da uno in modulo e segno, fornendo il risultato in complemento a 2.

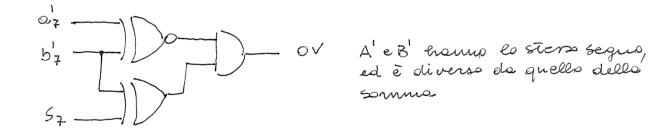

- b) Realizzare la rete che valuta l'overflow nella sottrazione precedente.

# ESERCIZIO N°3

5 punti

Dati i numeri A = 3.7 B = -22.4 e C = -0.09

- a) Determinare le caratteristiche della loro rappresentazione su 8 bit in virgola fissa e in MS, che presenta il minimo errore assoluto; valutare in ogni caso l'errore relativo.

- **b)** Determinare la rappresentazione di *A*, *B* e *C* in virgola mobile in formato standard IEEE 754 singola precisione e valutare anche in questo caso l'errore di rappresentazione relativo.

# **ESERCIZIO Nº4**

4 punti

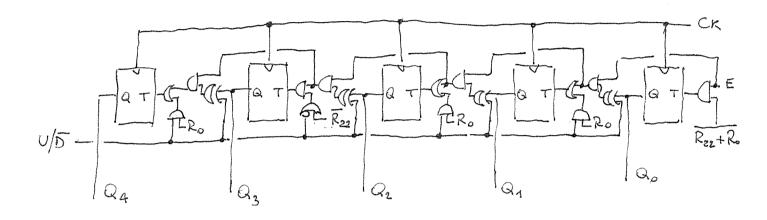

Progettare un contatore sincrono (up/down con abilitazione) modulo 23 facendo uso di T-FF.

# **ESERCIZIO N°5**

4 punti

Progettare una macchina sequenziale sincrona, con il minimo numero di flip-flop, secondo il modello di Moore con un ingresso e una uscita in grado di generare ogni volta che l'ingresso viene rilevato a 1 una sequenza pari a 010011. Durante la generazione della sequenza, l'ingresso non viene preso in considerazione. In assenza del comando di generazione, l'uscita della macchina deve restare a 0.

### ESERCIZIO Nº6

9 punti

Realizzare una subroutine per un microcontrollore della famiglia AVR che valuta il determinante di una matrice 3x3 contenuta in memoria, per righe, a partire dall'indirizzo contenuto in *Z*. Gli elementi della matrice sono singole cifre esadecimali e il risultato deve essere lasciato nella coppia di registri R1:R0. Esistono casi in cui il risultato non è rappresentabile?

Mappa di Karnongh

| CD 00 01 11 10 | ĭ |

|----------------|---|

| 00 (0) 10/10/  |   |

| 10/10/10/10/   | - |

| 01 0 1 1 1     |   |

| 11 1 1 1 1     |   |

| 10 1 0 0 0     |   |

Sintesi ottima PS Si eranno 3 implicati essenziali

$$Y = (A+B+C)(\overline{B}+D)(\overline{A}+D)$$

CNOT : 1 MS

€ OR3: 2MS

COR2: 1,5MS

CANDS: 2MS

Similatione

2) Per redittere la rête richiesta, si convertous entrambi i doti in complemento e 2 e si use un normale sottratione reditteto con full-edder

Rete per l'overflow

(3)

Per le parte intera con seguo sono necessari 6 bit (-31.. 31) Lessono quindi 2 bit per la parte frazioneria.

Rappresentazione MS (prrotondomento)

$$A=3,7$$

; 000011.11  $E_A=0,05$   $E_Z=1,35%$

$$B_{=}-22,4$$

; 110110.10  $\varepsilon_{A}=0,1$   $\varepsilon_{Z}=0,446%$

5: osseri l'inadequaterra delle rappresentazioni in virgola fisse per responsazione numeri con grande range dinamico (repporto tra max e min modues)

Si ricorde che

$$\varepsilon_A = |x - \hat{x}|$$

e  $\varepsilon_R = \frac{\varepsilon_A}{|x|}$

(m moterioue IEEE 754 (binery 32) si ere

$$-22.4 = (-1)^{1} 2^{4} (1 + 0.4 \cdot 2^{23} \cdot 2^{-23})$$

$$= 131$$

$$= 3355443$$

$$[1|10000011|011.0011.0011.0011.0011]$$

$$-0.09 = (-1)^{1} 2^{-4} (1+0.44 \cdot 2^{23} \cdot 2^{-23})$$

$$= 123$$

$$= 3690988$$

$$[1]01111011.1000.0101.0001.1110.1100]$$

1 Partioure come bese de un contotore module 32 con abilitatione Osseriano le commute zioni

L'essetto di modifica è condizionato dal seguale UID

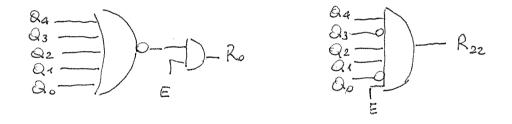

# (5) grafo di flusso

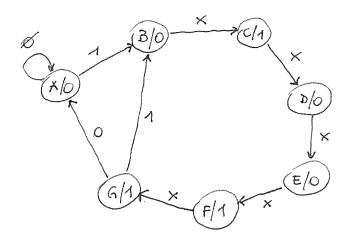

Per la codifica degli steti, si è scelto di semplificare la rete per l'uscita (U=90)

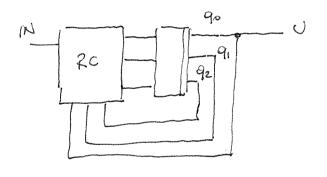

Architetture

Occorrono 3 FF e non ci soup sisti equivolenti

Codifice degli stati

Peie per lo sisto fui uro

| VIN.                                   | 92  |     |     |      |

|----------------------------------------|-----|-----|-----|------|

| 9.90                                   | .00 | 01  | 11_ | 10   |

| 00                                     | 000 | 101 | 101 | 010  |

| 01                                     | -   | 111 | 111 |      |

| ************************************** | 110 | 000 | 010 | 110  |

| 10                                     | 011 | 100 | 100 | 01-1 |

# 6

Realizzare una subroutine per un microcontrollore della famiglia AVR che valuta il determinante di una matrice 3x3 contenuta in memoria, per righe, a partire dall'indirizzo contenuto in Y. Gli elementi della matrice sono singole cifre esadecimali e il risultato deve essere lasciato nella coppia di registri R1:R0. Esistono casi in cui il risultato non è rappresentabile?

```

/* Non si hanno problemi di rappresentabilità in quanto il risultato (in modulo)

è sicuramente minore di 2*15^3=6750 (15,15,0,0,15,15,15,0,15).

det3x3:

push R2 //salva i registri usati

push R3

push R16

push R17

.push R18

ldd R16,Z+0 //a11

ldd R17, Z+4 //a22

ldd R18, Z+8 //a33

mul R16, R17

mul R0,R18 //il primo prodotto al massimo dà 225

movw R3:R2,R1:R0

ldd R16,Z+1 //a12

ldd R17, Z+5 //a23

ldd R18, Z+6 //a31

mul R16, R17

mul R0, R18

add R2, R0

adc R3,R1

ldd R16, Z+2 //a13

ldd R17,Z+3 //a21

ldd R18, Z+7 //a32

mul R16, R17

mul R0, R18

add R2, R0

adc R3, R1

ldd R16, Z+2 //a13

ldd R17, Z+4 //a22

ldd R18, Z+6 //a31

mul R16, R17

mul R0, R18

sub R2, R0

sbc R3,R1

ldd R16, Z+0 //a11

ldd R17, Z+5 //a23

ldd R18, Z+7 //a32

mul R16, R17

mul R0, R18

sub R2, R0

sbc R3,R1

```

```

ldd R16,Z+1 //a12

ldd R17,Z+3 //a21

ldd R18,Z+8 //a33

mul R16,R17

mul R0,R18

sub R2,R0

sbc R3,R1

movw R1:R0,R3:R2

pop R18 //rispristina i registri

pop R17

pop R16

pop R3

pop R2

ret

```