| SCHEDA ASE1702 |      | Data: 3 Febbraio 2017 |

|----------------|------|-----------------------|

| Cognome        | Nome |                       |

## ESERCIZIO Nº1

8 punti

Realizzare un sottoprogramma per il microcontrollore AVR XMEGA256A3BU, che trasferisce un blocco di n interi su 2 byte (n è contenuto in R16 e il valore 0 deve essere interpretato come 256) collocati in memoria a partire dall'indirizzo X in una nuova posizione il cui primo indirizzo è contenuto in Y.

## ESERCIZIO N°2

5 punti

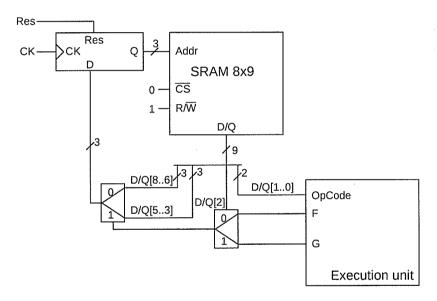

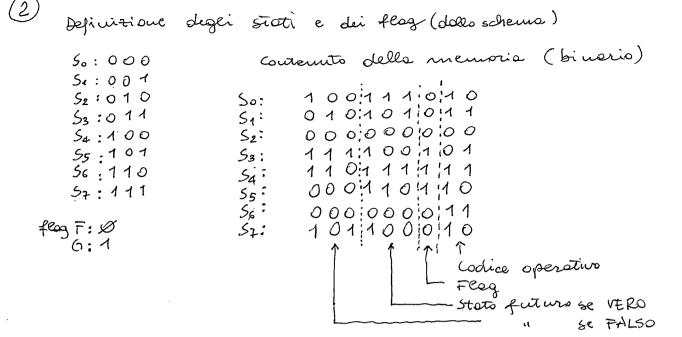

Determinare il diagramma di flusso, attribuendo agli stati un nome a scelta, del seguente sequenziatore. Il contenuto della SRAM è costituito dalle 8 parole esadecimali: 0x13A, 0x0AB, 0x000, 0x1E5, 0x1BF, 0x036, 0x003, 0x162. Sarebbe stato possibile realizzare il sequenziatore con un contatore a caricamento parallelo, risparmiando sulla dimensione della SRAM (spiegare)?

#### **ESERCIZIO N°3**

5 punti

Disegnare lo schema logico di un contatore Johnson modulo 7. Si hanno a disposizione D-FF e porte logiche elementari (AND, OR, NOT). L'uscita, su 7 bit, deve presentare la sequenza {1000000; 0100000; 0010000; 0001000; 0000010; 0000001}. Discutere le conseguenze sul circuito del valore dello stato iniziale, in particolare individuando per ogni caso dopo quanti cicli di clock la macchina inizia a comportarsi correttamente.

#### ESERCIZIO Nº4

6 punti

- a) Determinare la mappa di Karnaugh di una funzione logica  $Z = f(X_4, X_3, X_2, X_1, X_0)$  dove  $X_4, X_3$  e  $X_1, X_0$  rappresentano 2 cifre consecutive in codifica GRAY, mentre  $X_2$  è un bit di parità (logica parità **dispari**); Z vale 1 se si verifica almeno una di queste condizioni: la codifica GRAY non è rispettata; la regola di parità non è corretta (Zvale 0 altrimenti).

- **b)** Realizzare con circuito a porte logiche AND, OR, NOT e 2 livelli di logica la funzione del punto a) sia in forma PS sia in forma SP.

- c) Se porte logiche elementari (AND, OR, NOT) a K ingressi hanno  $T_{pd} = 0.05$  ns + 0.1 K ns, quale è il  $T_{pd}$  massimo dei due circuiti di cui al punto b)? Se ingressi e uscite del più veloce dei 2 circuiti combinatori di cui al punto b) sono registrati con registri aventi  $T_{co} = 0.15$  ns,  $T_{hold} = 0.05$  ns e  $T_{setup} = 0.1$  ns quale è la massima frequenza di lavoro possibile?

## **ESERCIZIO N°5**

4 punti

Realizzare la funzione logica  $Z = f(X_4, X_3, X_2, X_1, X_0)$  di cui all'esercizio 4

- a) tramite multiplexer;

- **b)** tramite decoder.

#### ESERCIZIO N°6

5 punti

Dati i numeri  $X = -\pi + 1$ ,  $Y = -\sqrt{3}$ , Z = -13/8 e ipotizzando che sia accettabile un errore minore o uguale a  $10^{-1}$  sulla parte frazionaria

- a) Determinare il numero minimo di bit per raggiungere la specifica e la loro rappresentazione in virgola fissa e MS.

- **b)** Determinare la loro rappresentazione in virgola mobile formato standard IEEE 754 singola precisione (binary32).

- c) Se si usa il microcontrollore AVR XMEGA analizzato durante il corso, quale errore si commette nel rappresentare in un registro i numeri di cui sopra?

# 1

Realizzare un sottoprogramma per il microcontrollore AVR XMEGA256A3BU, che trasferisce un blocco di n interi su 2 byte (n è contenuto in R16 e il valore 0 deve essere interpretato come 256) collocati in memoria a partire dall'indirizzo X in una nuova posizione il cui primo indirizzo è contenuto in Y.

```

sposta:

push R16 //salva registri

push R17

push XL

push XH

push YL

push YH

clr R17

cp XL,YL //individua se c'e` rischio di sovrascrittura

cpc XH, YH

brsh loop1

add XL,R16 //in questo caso si parte dal fondo

adc XH, R17

add YL,R16

adc YH, R17

rjmp loop2

loop1: //X segue Y: non si puo` sovrascrivere

ld R17,X+ //trasferisce la parte bassa

st Y+, R17

ld R17,X+ //trasferisce la parte alta

st Y+, R17

dec R16

brne loop1

rjmp end

loop2: //X precede Y e i puntatori sono in fondo

ld R17,-X //trasferisce la parte alta

st -Y,R17

ld R17,-X //trasferisce la parte bassa

st -Y, R17

dec R16

brne loop2

end:

pop YH //ripristina i registri modificati

pop YL

pop XH

pop XL

pop R17

pop R16

ret

```

Diogramme di flusso

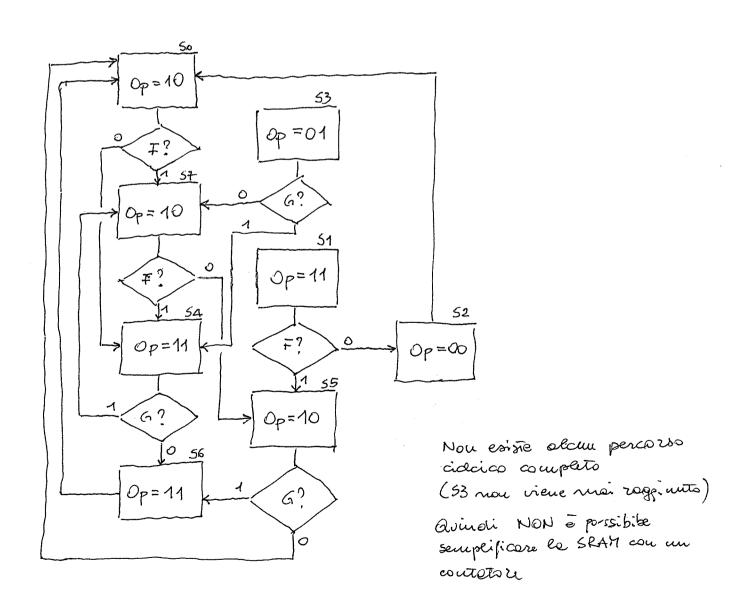

## Johnson Counter Hodulo 7

Sequents degli stati pariendo della conditione unela

| Stoto | Q <sub>A</sub> | Qz | 6 | 10 € | ه(   |   |       |

|-------|----------------|----|---|------|------|---|-------|

| Sp    | 0              | 0  | 0 | 0    |      |   |       |

| Sg    | 0              | 0  | 0 | 0    |      |   |       |

| 5.    | 1 1 0 0        | 1  | 0 | 0    |      |   |       |

| SE    | 1              | 1  | 1 | 0    |      |   |       |

| 57    | 0              | 1  | 1 | 1    |      |   |       |

| 53    | 0              | 0  | 1 | 1    |      |   |       |

| 51    |                | 0  | 0 | 1    |      |   |       |

|       | 0              | 0  | 0 | 0    | dopo | 7 | 570ti |

Generazione dell'uscitz

Our onvente partends de uns quelsies degli stati delle sequentes, il comportaments appore colletto Esaminiones l'evoluzione a pertire dei rimonenti 9 stati

si torne a So

⇒

$$\frac{52}{9}$$

0 0 1 0 (1 ciclo e poi 0k)

$\frac{54}{9}$  0 0 0 1 0 0 (4 cicli e poi 0K)

⇒  $\frac{54}{9}$  0 1 0 1 0 (3 cicli e poi 0K)

⇒  $\frac{55}{9}$  0 1 0 1 (2 cicli e poi 0K)

$\frac{52}{9}$  0 0 1 0 redi

$\frac{53}{9}$  0 0 1 1 0 (1 ciclo e poi 0K)

$\frac{53}{9}$  1 0 0 1 (5 cicli e 0K)

$\frac{54}{9}$  0 1 0 0 redi

→

$$\frac{58}{55}$$

| 1011 (3 cicli e OK)

$\frac{55}{55}$  | 0101 resli

→  $\frac{5}{56}$  | 1100 (1 ciclo e OK)

$\frac{7}{56}$  | 1110 OK

$\frac{7}{57}$  | 1111 (1 ciclo e OK)

$\frac{57}{57}$  | 0111 OK

$$x = -2,14159...$$

$y = -1,73205...$   $z = -1,625$

a) Se adottions una strategia di orrotondomento, per ottenere un errore inferiore a 0,1 sulla parte frazioneria, servono in generale, 3 bit.

Avremo sempre -1/16 & Ea < 1/16.

Quindi, in MS servizarurs 1 bit per il seguo 2 bit per la parte intera 3 bit per la parte frazionerio

Nei cesì perticolori si ha

$$X = 1 | 10,001 \qquad (-2,125 \qquad \epsilon_{A} = -0,0166_{-})$$

$$Y = 1 | 01,110 \qquad (-1,750 \qquad \epsilon_{A} = 0,0014_{-})$$

$$Z = 1 | 01,101 \qquad (-1,625 \qquad \epsilon_{A} = \phi)$$

b) Rappresentatione binary 32  $\times = (-1)^5 2^{e-127} \left\{ 1 + \sum_{i=1}^{23} b_{23-i} \sum_{i=1$

$$-2,14159... = (-1)^{1}2^{1}(1+593883\cdot 2^{-23})$$

[arrotoud\_]

$-1,73205... = (-1)^{1}2^{\circ}(1+6140887\cdot 2^{-23})$

5 e=127 [1]0111111|1011101101100111001111]

$$-1,625 = (-1)^{1} \cdot 2^{\circ} \left(1 + 5242880 - 2^{-23}\right)$$

c) la rappresentatione nell'XITEGA è su 8 bit in complements a 2. Posso aggingere 2 bit alla parie frazioneria.

$$X = 1/10,00101$$

MS

$101,11010$  C1

$101,11011$  C2  $-3,15625$

$\varepsilon_{A} = 0,01466$   $\varepsilon_{R} = 6,84\%$   $\{1\varepsilon_{a}/x\}$

$$\gamma = 1101,10111$$

HS

$110,0100$  C1

$110,01001$  C2 -1,71875

$\epsilon_{A} = -0,0133$   $\epsilon_{2} = 7,68\%$ .  $\{|\epsilon_{2}/\gamma|\}$

$$z = 1101,10100$$

HS

$110,01011$  C1

$110,01100$  C2 -1,625

$\varepsilon_{A} = \phi$   $\varepsilon_{z} = \phi$

Per gli eserciti 4 e 5 si rimondo ai compiti preadenti